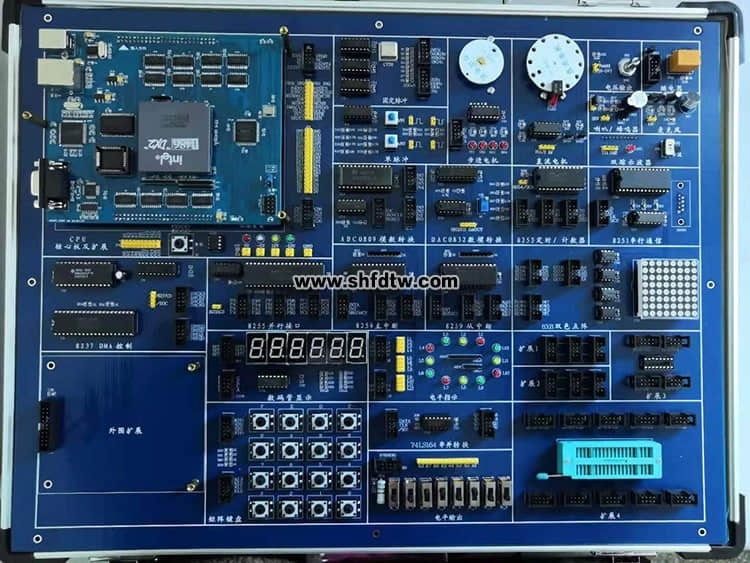

TW-X35綜合型計算機組成原理實驗係統

一、結構特點

本係統由鋁木合金箱體、高性能穩壓電源、係統控製部件、開放式實驗電路區等組成。全部實驗用信號線的連接采用排線,操作方便,接觸可靠。基礎實驗基於中小規模集成電路,綜合性實驗基於在係統可編程核心器件,資源完全向學開放,可以完成“計算機組成原理”、“計算機結構與邏輯設計”、“在係統編程”、“VHDL設計”、“電子係統綜合設計”等課程的實驗,並可以進行“專用集成電路設計”的驗證實驗。本實驗箱適用於本專科院校計算機專業和其它相關專業的相關課程的實驗和創新設計。

您隻要致電:021-55884001(袁經理)

我們可以解答 綜合型計算機組成原理實驗係統 的相關疑問!

我們可以幫您推薦符合您要求的 綜合型計算機組成原理實驗係統 實訓器材 教育教學設備 相關產品!

找不到所需產品?請點擊 產品導航頁

當前產品頁麵地址://m.yyh998.com/productshow-38-2395-1.html

二、技術性能

1、硬件係統采用高性能單片機89S52和LATTICE公司CPLD器件的有機結合,使係統的硬件控製電路精簡而可靠。

2、提供手動、自動和聯機三種工作方式,滿足不同層次實驗的監視需要。

3、具有完善的係統檢測電路和係統保護電路設計,使實驗係統更易於維護和使用。

4、係統自備雙通道邏輯示波器,便於實驗過程中時序信號的測量。

5、係統和電腦采用RS232/USB通信方式。

6、實驗係統采用總線結構,使實驗計算機具有結構簡單清晰、擴展方便、靈活易變等諸多優點,實驗時隻要少些接線即可。

7、擴展FPGA實驗模塊,實現複雜模型機的設計實驗。

8、專為本機配備的動態集成調試運行軟件以圖形化的界麵顯示模型機內部數據的流向和各種控製信號的狀態以及時序關係。

三、硬件技術指標

1、實驗電路工作電源:+5V/2A、±12V/0.5A,每路均帶有短路保護和自動關斷功能,每路帶電源指示。其中+5V電源設計有過壓、過流、欠壓保護功能,待電路中故障排除後,自動恢複供電,確保設備和人身安全。

2、實驗係統的字長為8位。

3、實驗係統的基本指令係統類PC 機,有多種指令格式,多種尋址方式。

4、主存儲器采用8K字節靜態存儲器6264,用於存放用戶程序和數據。

5、配運算器模塊,由4片4位的算術邏輯單元功能發生器級聯而成。每片內實現16種二進製算術運算及16種邏輯運算,可進行8位、16位運算器實驗。

6、控製器采用微程序方案實現,控存字長為24位,可用最大容量為1024字節,且用電可擦寫的E2ROM存儲器芯片組成,支持動態微程序設計。

7、實驗係統工作頻率源由555時基電路和74LS123可再觸發單穩態多諧振蕩器組成產生,頻率範圍為330HZ~580HZ。可以同時產生四種不同時序的時鍾信號。

8、實驗係統配有微程序手動輸入並顯示模塊,裝有24個微程序輸入開關,用於輸入微程序。

9、配有手動16位數據輸入模塊,裝有16個數據輸入開關,用於輸入16位數據。

10、配8個控製開關,2個微動開關,用於手動控製整機的運行和切換運行方式等。

11、配2位七段數碼管以顯示程序運行的結果。另配置6個數碼管,用於交通燈顯示。

12、配微地址發生器模塊和微地址顯示模塊、微地址控製模塊。

13、配數據總線顯示模塊,用於顯示數據總線上的動態數據。

14、配總線地址顯示模塊,用於顯示地址總線上的動態地址。

15、配有一個雙向通用移位寄存器,以實現邏輯移位功能。

16、具有超前進位控製邏輯。

17、配有指令寄存器和地址寄存器。

18、主機上設計有二片大規模 CPLD 和超強51單片機作為整機的主控器件,可以在完全自動方式下完成全部部件實驗和整機模型機設計實驗。

19、配有並行I/O接口電路8255,實現帶輸入輸出接口的模型機的設計。

20、配有定時/計數器接口電路8253。實現帶定時/計數器功能的模型機的設計。

21、配有中斷控製器8259。實現帶中斷功能的模型機的設計)。

22、配有雙端口存儲器IDT713200。

23、模數A/D和數模D/A轉換電路,實現數模和模數的轉換(C9JH有)。

24、擴展ALTERA EPM240核心模塊,實現具備多功能複雜模型機的設計實驗。

25、實驗的連接:模塊間實驗線路的連接:全部信號采用排線連接,操作簡便,實驗導線連接穩定可靠。

26、機箱:堅固型鋁合金框架,厚實的 ABS 塑料包角,參考外形尺寸 480×360×150mm。

四、軟件技術指標

1、實驗係統集成動態調試運行軟件。

2、詳盡的CAI課件,能將實驗原理、實驗目的、芯片、查詢等功能集於一體,便於多媒體教學;

3、極強的程序和微程序調試功能,有單步、斷點和連續等運行方式。

4、有程序和微程序讀寫功能。

5、以彩色流程圖方式全程監視程序的運行狀態和運行結果。

6、 用debug讀寫存貯菜單,對寄存器進行輸入數據和參數設置以及讀出目標輸出信息。

五、實驗項目(全部提供源程序)

1、基礎實驗

1)8位算術邏輯運算實驗

2)帶進位控製8位算術邏輯運算實驗

3)16位算術邏輯運算實驗

4)移位運算器實驗

5)存儲器實驗

6)微控製器實驗

2、設計性使用

1)總線控製實驗

2)硬布線控製器實驗

3)乘法器設計實驗

4)FIFO先進先出存儲器實驗

5)數據通路實驗

6)基本模型機的設計與實現

7)擴展8255並行口實驗

8)擴展8253定時/計數器實驗

9)擴展8259中斷控製器實驗

10)擴展0809 AD轉換實驗

11)擴展0832 DA轉換實驗

12)擴展雙端口存儲器IDT713200實驗

3、綜合設計應用實驗

1)帶移位運算的模型機的設計與實現

2)複雜模型機的設計與實現

3)可重構原理計算機組成設計實驗

4)基於CISC和RISC處理器構成的實驗計算機的設計與實現

5)用大規模芯片在模型機的基礎上設計一個8位輸入輸出並行接口芯片8212。

6)基於流水技術構成模型計算機的實驗

六、實驗箱配置表

|

序號 |

名稱 |

說明 |

數量 |

|

1 |

DVCC-C9JH實驗主機箱 |

含詳細技術指標裏全部軟硬件 |

1台 |

|

2 |

杜邦8芯排線 |

40cm |

5根 |

|

3 |

杜邦5芯排線 |

40cm |

2根 |

|

4 |

杜邦4芯排線 |

40cm |

2根 |

|

5 |

交流電源線1根 |

長1.5米 |

1根 |

|

6 |

軟件光盤 |

聯機調試軟件和實驗例程 |

1套 |

|

7 |

實驗指導書 |

|

1套 |